# Sidekiq™ X2

RF Transceiver • High Performance

# HARDWARE USER MANUAL

V1.0 - NOVEMBER 11, 2020

# CHANGELOG

| Revision | Date       | Description                                                                                     | Author  |

|----------|------------|-------------------------------------------------------------------------------------------------|---------|

| 0.1      | 2017-08-10 | Pre-release draft, initial version                                                              | Barry L |

| 0.2      | 2017-09-07 | Subtandital updates in content; Added full pin map; Added Rx pre-select filter plot             | Barry L |

| 0.3      | 2017-09-15 | Updates after internal review; ready for public release                                         | Barry L |

| 0.4      | 2020-03-09 | Updated sections 7.1, 7.3, 8, 8.7, 8.8, 10.2, 10.3, 11, table12. Added table 3, sections 13, 14 | Barry L |

| 1.0      | 2020-11-11 | Markdown conversion, table updates                                                              | Barry L |

# DISCLAIMER

Epiq Solutions is disclosing this document ("Documentation") as a general guideline for development. Epiq Solutions expressly disclaims any liability arising out of your use of the Documentation. Epiq Solutions reserves the right, at its sole discretion, to change the Documentation without notice at any time. Epiq Solutions assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Epiq Solutions expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information. THE DOCUMENTATION IS DISCLOSED TO YOU "AS IS" WITH NO WARRANTY OF ANY KIND. EPIQ SOLUTIONS MAKES NO OTHER WARRANTIES, WHETHER EXPRESSED, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY RIGHTS. IN NO EVENT WILL EPIQ SOLUTIONS BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

# TABLE OF CONTENTS

| Introduction                                                                                                                                                                                                  | 6                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Legal Considerations                                                                                                                                                                                          | 7                                            |

| Proper Care and Handling                                                                                                                                                                                      | 8                                            |

| References                                                                                                                                                                                                    | 9                                            |

| Terms and Definitions                                                                                                                                                                                         | 10                                           |

| Hardware Overview                                                                                                                                                                                             | 12                                           |

| Hardware Specification         RF Receiver Specification (Rx1, Rx2, ObsRx)         RF Transmitter Specification (Tx1, Tx2)         Clock/Synchronization Specification         Hardware Specification         | 15<br>16                                     |

| Hardware Interfaces         Tri-Color Status LED         J1 (Rx2)         J2 (Rx1)         J3 (ObsRx)         J4 (Tx1)         J5 (Tx2)         Input - 10 MHz         PPS Input         RF Shield + Heatsink | 18<br>19<br>19<br>19<br>19<br>19<br>20<br>20 |

| VITA 57.1 HPC Connector         Supplemental Heat Transfer Surface                                                                                                                                            |                                              |

| FMC Pin Map         FMC Low Pin Count (LPC) Section         FMC High Pin Count (HPC) Section                                                                                                                  |                                              |

| Basic Usage in a Host System<br>Host System Compatibility<br>Operating System Compatibility<br>Power Consumption<br>Thermal Dissipation<br>JTAG Access on Sidekiq                                             | 36<br>36<br>37                               |

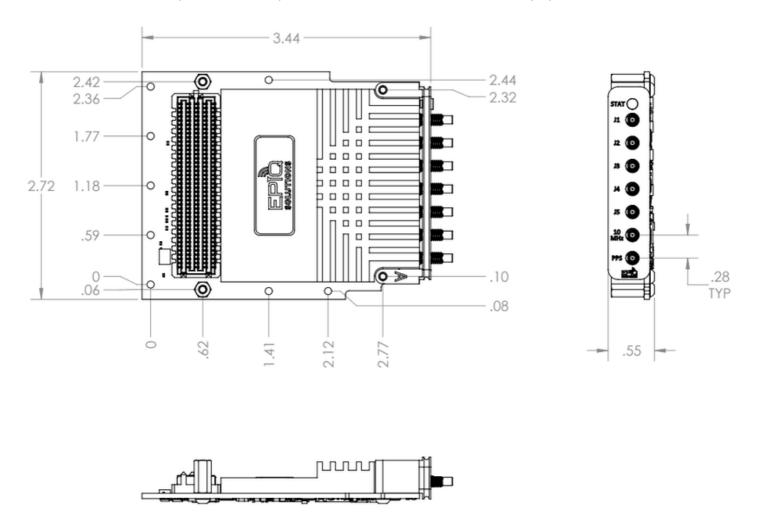

| Sidekiq X2 Mechanical Outline                                                                                                                                                                                 | 40                                           |

| Sidekiq X2 Thunderbolt 3 Platform Overview Basic Usage the Sidekiq X2 Thunderbolt 3 Platform                                                                                                                  |                                              |

| Accessing JTAG on the Sidekiq X2 T  | hunderbolt 3  | Platform | <br> | <br> | 43 |

|-------------------------------------|---------------|----------|------|------|----|

| Appendix A - Sidekiq X2 Statement o | of Volatility |          | <br> | <br> | 46 |

| Appendix B - Failure Rate & MTBF    |               |          | <br> | <br> | 47 |

# INTRODUCTION

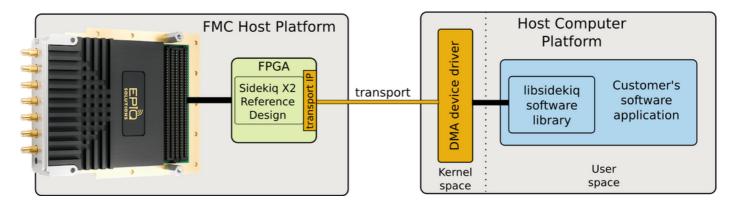

This document provides an overview and usage details of Epiq Solutions' Sidekiq X2 multichannel RF transceiver card [1], a VITA 57.1 compliant FPGA mezzanine card (FMC) utilizing the high pin count (HPC) interface. Sidekiq X2 provides the entire "antenna-to-bits" high performance RF signal chain in a single card, allowing a customer to radically shorten their typical RF platform development cycle. Sidekiq X2 can interface to any FMC HPC host system, where an FPGA and additional follow on processing would be executed. Epiq Solutions provides an FPGA reference design as well as software drivers, libraries, and test applications to demonstrate the usage of Sidekiq X2 interfaced to a COTS FMC host platform with a PCIe interface to a host computing system. This reference design, as well as the software drivers, libraries, and test applications, can then be ported to other FMC host carrier systems for custom deployment scenarios.

The following topics will be discussed:

- Overview of the Sidekiq X2 hardware interfaces

- Sidekiq X2 usage/integration options

- Sidekiq X2 example usage in the FMC host platform reference design

All documentation and support for Sidekiq X2 is provided through Epiq Solutions' support website [2], please note that it is necessary to register prior to accessing the relevant information for your purchase.

# LEGAL CONSIDERATIONS

The Sidekiq X2 is distributed all over the world. Each country has its own laws governing reception and transmission of radio frequencies. Each user of Sidekiq X2 and associated software is solely responsible for insuring that it is used in a manner consistent with the laws of the jurisdiction in which it is used. Many countries, including the United States, prohibit the transmission and reception of certain frequency bands, or receiving certain transmissions without proper authorization. Again, the user is solely responsible for the user's own actions.

# PROPER CARE AND HANDLING

Each Sidekiq X2 card is fully tested by Epiq Solutions before shipment, and is guaranteed functional at the time it is received by the customer, and ONLY AT THAT TIME. Improper use of the Sidekiq X2 card can cause it to become non-functional. In particular, a list of actions that may cause damage to the hardware include the following:

- Handling the unit without proper static precautions (ESD protection) when the housing is removed or opened up

- Inserting or removing Sidekiq X2 from a host system when power is applied to the host system

- Connecting a transmitter to the RX port without proper attenuation

- Executing custom software and/or an FPGA bitstream that was not developed according to guidelines

The above list is not comprehensive, and experience with the appropriate measures for handling electronic devices is required.

# REFERENCES

1. Sidekiq X2 Product Page

https://epiqsolutions.com/rf-transceiver/sidekiq-x2

2. Epiq Solutions Support Page

https://support.epiqsolutions.com

3. VITA website

https://www.vita.com

4. Analog Devices' AD9371 Wideband Transceiver Product Page

http://www.analog.com/en/products/rf-microwave/integrated-transceivers-transmitters-receivers/wideband-transceivers-ic/ad9371.html

5. HiTech Global's Product Page for the HTG-K800 FPGA PCIe Carrier Card

http://www.hitechglobal.com/Boards/Kintex-UltraScale.htm

# **TERMS AND DEFINITIONS**

| Term  | Definition                                                       |

|-------|------------------------------------------------------------------|

| A/D   | Analog to Digital converter                                      |

| D/A   | Digital to Analog converter                                      |

| dB    | Decibel                                                          |

| dBm   | Decibels (dB) with reference to one milliwatt (mW).              |

| ESD   | ElectroStatic Discharge                                          |

| FMC   | FPGA Mezzanine Card                                              |

| FPGA  | Field Programmable Gate Array                                    |

| GPS   | Global Positioning System                                        |

| HPC   | High Pin Count (a variant of the VITA 57.1 electrical interface) |

| I/Q   | In-Phase / Quadrature Phase                                      |

| JTAG  | Joint Test Action Group                                          |

| KHz   | Kilohertz                                                        |

| LED   | Light Emitting Diode                                             |

| LFM   | Linear Feet per Minute                                           |

| LNA   | Low Noise Amplifier                                              |

| LPC   | Low Pin Count (a variant of the VITA 57.1 electrical interface)  |

| MHz   | Megahertz                                                        |

| MMCX  | Micro-Miniature Coaxial RF Connector                             |

| ObsRx | Observation Receiver                                             |

| PC    | Personal Computer                                                |

| PDK   | Platform Development Kit                                         |

| PPS   | Pulse Per Second                                                 |

| RF    | Radio Frequency                                                  |

| Rx    | Receive                                                          |

| SDK   | Software Development Kit                                         |

| SDR   | Software Defined Radio                                           |

| SMP   | Sub-Miniature push-on RF connector                               |

| SSH   | Secure SHell                                                     |

| SSMC | A smaller version of the SubMiniature type C RF connector                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------|

| тсхо | Temperature Compensated Crystal Oscillator                                                                               |

| Тх   | Transmit                                                                                                                 |

| UART | Universal Asynchronous Receiver Transmitter                                                                              |

| USB  | Universal Serial Bus                                                                                                     |

| VITA | The standards body governing a variety of electro-mechanical specifications for computing systems (see [3] for details). |

Table 1: Terms and Definitions

# HARDWARE OVERVIEW

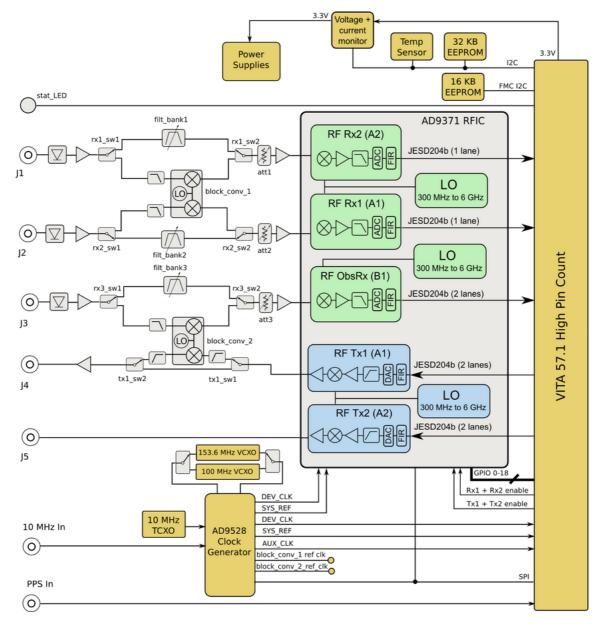

Sidekiq X2 is a high performance multichannel RF transceiver card providing a complete "antennato-bits" solution in a VITA 57.1 FPGA mezzanine card (FMC) form factor. Sidekiq X2 leverages Analog Devices' AD9371 wideband transceiver RFIC [4] to provide the core functionality of the card. The capability of the card is further enhanced with on-board circuitry to extend the RF tuning range, provide RF pre-select filtering on the RF receivers, support external synchronization inputs, and other features only found on Sidekiq X2. The key highlights of Sidekiq X2 are enumerated below:

- VITA 57.1 FMC compliant card providing a high pin count (HPC) interface

- RF tuning range from 1 MHz to 6 GHz

- Phase coherent RF receiver pair with common LO

- Third independently tunable RF receiver

- Phase coherent RF transmitter pair with common LO

- Supports RF channel bandwidths up to 100 MHz

- 16-bit A/D converters supporting sample rates up to 122.88 Msamples/sec

- 14-bit D/A converters supporting sample rates up to 245.76 Msamples/sec

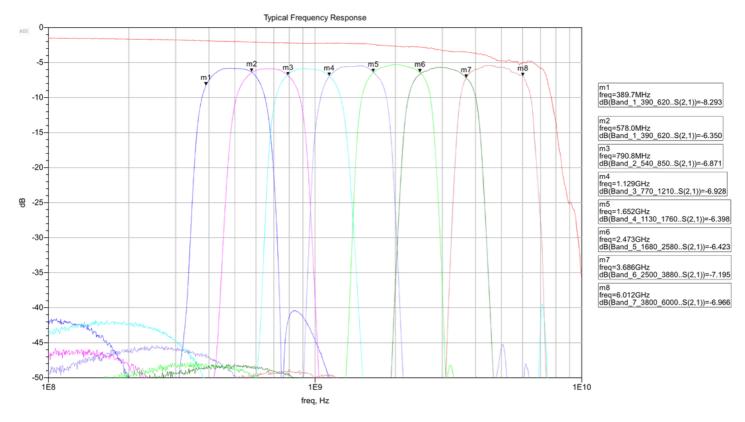

- Seven-band RF pre-select filters on all RF receivers

- On-board 10 MHz TCXO reference clock (0.2 PPM stability)

- Accepts external 10 MHz and PPS inputs for synchronization to user provided reference signals

- Weight: 2.7 oz

- Power: 4-10 W (application dependent)

- Size: 84.1mm x 69mm

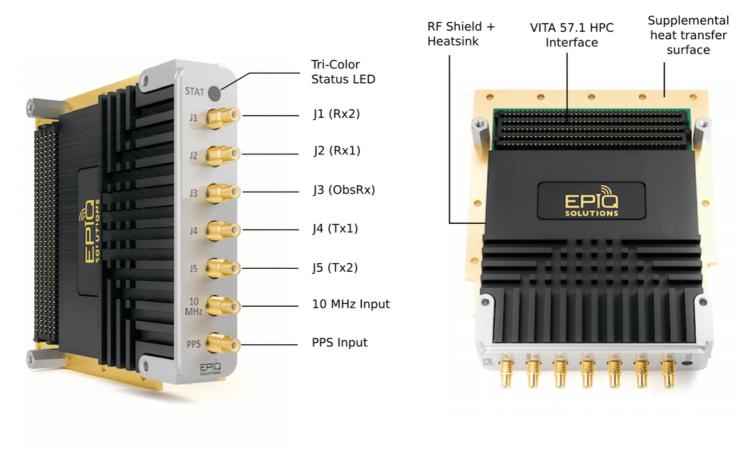

Figure 1: Sidekiq X2 card (with heatsink / RF shield installed)

Figure 2: Sidekiq X2 block diagram

# HARDWARE SPECIFICATION

### **RF RECEIVER SPECIFICATION (RX1, RX2, OBSRX)**

|                                      | -                                                                                        |

|--------------------------------------|------------------------------------------------------------------------------------------|

| RF Input                             | 50 ohms (MMCX, SMP and SSMC options)                                                     |

| Architecture                         | Zero-IF (direct conversion)                                                              |

| Tuning Range                         | 75 MHz to 6 GHz, able to capture 1 MHz to 6 GHz                                          |

| Tuning Step Size                     | 2.3 Hz                                                                                   |

| Tuning Time                          | $\sim$ 1 ms to 2.5 ms, contact Epiq Solutions' support [2] for more detailed information |

| Typical Noise Figure                 | 6-8 dB below 3 GHz, 8-10 dB above 3 GHz                                                  |

| Spurious-Free Dynamic Range          | ~ 70 – 80 dB typical                                                                     |

| Typical IIP3 (at 8 dB noise figure)  | +5 to +10 dBm                                                                            |

| Gain Control Range                   | 0 to 30 dB (Rx1 and Rx2); 0-18 dB (ObsRx); 1 dB steps                                    |

| Gain Control Modes                   | Manual or AGC                                                                            |

| A/D Converter Sample Rate            | Up to 122.88 Msamples/sec                                                                |

| A/D Converter Sample Width           | 16 bits                                                                                  |

| Typical I/Q Balance                  | 70 dB                                                                                    |

| A/D JESD204b Lane Rate               | Up to 6.144 Gbps                                                                         |

| # of JESD204b Lanes Utilized         | Rx1, Rx2: 1 lane ObsRx: 1 or 2 lanes (Fs dependent)                                      |

| Max RF input signal (without damage) | +25 dBm                                                                                  |

| RF full scale input (at max gain)    | ~ -30 dBm to -20 dBm, (frequency dependent)                                              |

| RF Pre-Select Filter Passbands       | Automatically selected when tuning the RF receiver; see Figure 3 for passband details    |

|                                      |                                                                                          |

Table 2: rx specification

## **RF TRANSMITTER SPECIFICATION (TX1, TX2)**

| RF Output    | 50 ohms (MMCX, SMP and SSMC options) |

|--------------|--------------------------------------|

| Architecture | Zero-IF (direct conversion)          |

| Tuning Range                    | Tx1: 1 MHz* to 6 GHz<br>Tx2: 300 MHz to 6 GHz<br>*Tx1 transmit frequency between 1 MHz and 300 MHz shares an LO source for block<br>conversion with the ObsRx port |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tuning Step Size                | 2.3 Hz                                                                                                                                                             |

| Tuning Time                     | $\sim$ 1 to 2.5 ms, contact Epiq Solutions' support [2] for more detailed information                                                                              |

| Gain Control Range              | 0 to 42 dB, 1 dB steps                                                                                                                                             |

| Max RF Transmit Output<br>Power | Tx1: +10 dBm to +15 dBm (<3 GHz)<br>+3 dBm to +10 dBm (>3 GHz)<br>Tx2: 0 dBm to +3 dBm (<3 GHz)<br>-10 dBm to 0 dBm (>3 GHz)                                       |

| Typical OIP3                    | +26 dBm                                                                                                                                                            |

| D/A Converter Sample<br>Rate    | Up to 245.76 Msamples/sec                                                                                                                                          |

| D/A Converter Sample<br>Width   | 14 bits                                                                                                                                                            |

| Typical I/Q Balance             | >60 dB                                                                                                                                                             |

| D/A JESD204b Lane<br>Rate       | Up to 6.144 Gbps                                                                                                                                                   |

| # of JESD204b Lanes<br>Utilized | Tx1: 1 or 2 lanes (sample rate dependent)<br>Tx2: 1 or 2 lanes (sample rate dependent)                                                                             |

Table 3: tx specification

## **CLOCK/SYNCHRONIZATION SPECIFICATION**

| Port                                       | 50 ohms (MMCX, SMP and SSMC options)                                                                                                                         |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On Board Reference Clock                   | 40 MHz TCXO (0.2 PPM stability) Part #: Abracon ASVTX12                                                                                                      |

| External Reference Clock Input Frequency   | 10 MHz                                                                                                                                                       |

| External Reference Clock Input Power Range | -5 dBm to +10 dBm                                                                                                                                            |

| On Board VCXO for DEV_CLK                  | Software switchable between two options (both populated on board):<br>Option 1: 153.6 MHz (PN: Bliley BCVCB153M6)<br>Option 2: 100 MHz (PN: Bliley BCVCB100) |

| PPS Input Level                            | Vadj logic level (1.8V or 2.5V), 5V tolerant                                                                                                                 |

Table 4: clock/sync specification

| Component Temperature Rating | -40 deg C to +85 deg C                                                         |

|------------------------------|--------------------------------------------------------------------------------|

| FMC Interface Type           | High Pin Count                                                                 |

| FMC Card Dimensions          | 84.1 mm x 69 mm                                                                |

| FMC Stacking Height          | 8.5 mm                                                                         |

| Weight                       | 2.7 oz                                                                         |

| Temperature Sensor           | -55 deg C to +125 deg C (+/- 2 deg C resolution) P/N: Texas Instruments TMP100 |

| FMC (12P0V)                  | +12 V                                                                          |

| FMC (P3V3)                   | +3.3 V                                                                         |

| FMC Vadj Support             | 1.8V or 2.5V                                                                   |

#### Table 5: hardware specification

Figure 3: Rx pre-select filter passband plot (filtering used on Rx1, Rx2, and ObsRx)

# HARDWARE INTERFACES

Sidekiq X2 provides is a standard VITA 57.1 compliant FMC card, and thus has a specific set of externally accessible hardware interfaces that are available to a user when the card is integrated into a system. Each of these hardware interfaces are enumerated in Figure 4, and are defined below.

Figure 4: Sidekiq X2 user accessible I/O

### **TRI-COLOR STATUS LED**

The Tri-Color Status LED is a triple LED capable of emitting red, green, and blue light through the front panel light pipe. This LED is controlled through three GPIO signals (one for each color) accessible through the VITA 57.1 electrical interface. By default, this LED illuminates blue to indicate the card is powered up.

## J1 (RX2)

The J1 (Rx2) interface is an SSMC jack connector that provides an RF input path for the Rx2 antenna port. This antenna port is capable of receiving signals between 1 MHz and 6 GHz. The RF

receiver associated with this antenna port shares a common LO with J2 (Rx1). The impedance of this port is 50 ohms. This port is also referenced by its handle name (RxA2) in the libsidekiq API.

### J2 (RX1)

The J2 (Rx1) interface is an SSMC jack connector that provides an RF input path for the Rx1 antenna port. This antenna port is capable of receiving signals between 1 MHz and 6 GHz. The RF receiver associated with this antenna port shares a common LO with J1 (Rx2). The impedance of this port is 50 ohms. This port is also referenced by its handle name (RxA1) in the libsidekiq API.

### J3 (OBSRX)

The J3 (ObsRx) interface is an SSMC jack connector that provides an RF input path for the ObsRx antenna port. This antenna port is capable of receiving signals between 1 MHz and 6 GHz, and can be tuned independently of Rx1 and Rx2. The impedance of this port is 50 ohms. This port is also referenced by its handle name (RxB1) in the libsidekiq API.

## J4 (TX1)

The J4 (Tx1) interface is an SSMC jack connector that provides an RF output path for the Tx1 antenna port. This antenna port is capable of transmitting signals between 1 MHz and 6 GHz, and shares a common LO with J5 (Tx2). The impedance of this port is 50 ohms. This port is also referenced by its handle name (TxA1) in the libsidekiq API.

## J5 (TX2)

The J5 (Tx2) interface is an SSMC jack connector that provides an RF output path for the Tx2 antenna port. This antenna port is capable of transmitting signals between 300 MHz and 6 GHz, and shares a common LO with J4 (Tx1). The impedance of this port is 50 ohms. This port is also referenced by its handle name (TxA2) in the libsidekiq API.

#### **INPUT - 10 MHZ**

The 10 MHz Input port is an SSMC jack connector that accepts an external 10 MHz input signal for the purpose of phase locking the on board reference clock. The acceptable signal level for this external 10 MHz input is between -5 dBm and +10 dBm. By default, Sidekiq X2 has an internal

reference clock on board that is used for phase locking the system. In order to use an external 10 MHz reference input, the libsidekiq software API provides a function call to disable on the on-board 10 MHz reference and lock on to this external 10 MHz reference input.

#### **PPS INPUT**

The PPS Input port is an SSMC jack connector that accepts a pulse per second (PPS) input signal for the purpose of providing a temporal frame of reference relative to this PPS edge. This PPS signal is routed through a SN74LVC2G17YZPR buffer directly to the FMC electrical interface, and thus routes directly into the FPGA on the host system. The PPS edge is expected to be a rising edge with a fast slew rate, with a logic level high defined as any voltage between 0.85V and 5V, dependent on Vadj (+1.8V / +2.5V). This PPS signal is used by the Sidekiq X2 FPGA reference design to latch the digital timestamp of when the PPS edge occurs in the FPGA, and can then be queried by the libsidekiq software API. It is also possible to coordinate other actions to take place based on the occurrence of a PPS edge, such as starting Rx or Tx streaming.

**Note:** for conduction cooled applications, MMCX or SMP connectors are available. Contact Epiq Solutions for details.

### **RF SHIELD + HEATSINK**

The RF shield/heatsink provides both RF isolation from spurious RF signals, while also providing a thermal dissipation path for the card when used in convection cooled application. A minimum air flow of TBD LFM is required to ensure that the heat generated by the card is adequately dissipated.

### **VITA 57.1 HPC CONNECTOR**

The VITA 57.1 HPC connector is the primary electrical interface for connecting Sidekiq X2 to a host system. The complete pin mapping for signals accessible through this HPC interface on Sidekiq X2 is defined in the FMC High Pin Count (HPC) Section..

Note: It is assumed that the standard Sidekiq X2 FPGA reference design + libsidekiq software API is being utilized by the host system. This reference design + software API provides all of the infrastructure and control necessary to control the operation of the card, as well as stream data between the card and the host system. The Sidekiq X2 FPGA reference design + libsidekiq software API can be ported to alternate host platforms other than the PDK reference platform. Please contact Epiq Solutions for details.

### SUPPLEMENTAL HEAT TRANSFER SURFACE

The Supplemental Heat Transfer Surface provides an additional thermal relief surface for the FMC card. This area surrounding the edge of the card is defined in the VITA 57.1 specification for the purpose of thermal relief, and can be used in conduction cooled deployments. For convection cooled deployments with the appropriate airflow moving over the RF shield + heatsink, this supplemental heat transfer surface is unused.

# FMC PIN MAP

The following table provides the definition of all of the pins utilized on the FMC interface of Sidekiq X2. This includes pins allocated to both the low pin count (LPC) portion of the connector, as well as the high pin count (HPC) portion of the connector. Additional details of the FMC electrical interface can be found in the VITA 57.1 specification [3]. Note: the definition and allocation of these pins typically have a specific meaning in the context of both the FMC specification, and more importantly, the Sidekiq X2 FPGA reference design delivered with the Sidekiq X2 PDK. Epiq Solutions provides support for Sidekiq X2 when used in conjunction with the Sidekiq X2 FPGA reference design and associated libsidekiq software library.

| FMC Signal<br>Name | FMC<br>Pin | FMC Description                                                        | Sidekiq X2 Net<br>Name | Description                                                                      | Logic<br>Standard,<br>I/O Type |

|--------------------|------------|------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------|--------------------------------|

| TRST_L             | D34        | JTAG reset                                                             |                        | N/C                                                                              |                                |

| ТСК                | D29        | JTAG clock                                                             |                        | N/C                                                                              |                                |

| TDO                | D31        | JTAG data out                                                          |                        | Connected to D30                                                                 |                                |

| TDI                | D30        | JTAG data in                                                           |                        | Connected to D31                                                                 |                                |

| TMS                | D33        | JTAG mode select                                                       |                        | N/C                                                                              |                                |

| SCL                | C30        | System mgmt I2C serial clock                                           | SCL_EEPROM             | I2C SCL for EEPROM per<br>FMC spec                                               | 3.3V,<br>In/Out                |

| SDA                | C31        | System mgmt I2C serial data                                            | SDA_EEPROM             | I2C SDA for EEPROM per<br>FMC spec                                               | 3.3V,<br>In/Out                |

| GA0                | C34        | Geographical address bit 0 for<br>EEPROM                               | GA0                    | Geographical address bit 0 for<br>EEPROM (pulled high,<br>EEPROM address = 0x53) | 3.3V, In                       |

| GA1                | C35        | Geographical address bit 1 for<br>EEPROM                               | GA1                    | Geographical address bit 1 for<br>EEPROM (pulled high,<br>EEPROM address = 0x53) | 3.3V, In                       |

| VREF_A_M2C         | H1         | Reference voltage for voltage signaling                                |                        | N/C                                                                              |                                |

| VREF_B_M2C         | K1         | Reference voltage for signaling                                        |                        | N/C                                                                              |                                |

| VIO_B_M2C1         | J39        | Voltage generated from<br>mezzanine card to power IO<br>bank B on FPGA |                        | Tied to Vadj                                                                     | DC, In                         |

## FMC LOW PIN COUNT (LPC) SECTION

| VIO_B_M2C0    | K40 | Voltage generated from<br>mezzanine card to power IO bank<br>B on FPGA |                | Tied to Vadj                                                    | DC,<br>In    |

|---------------|-----|------------------------------------------------------------------------|----------------|-----------------------------------------------------------------|--------------|

| GBTCLK1_M2C_N | B21 | Diff pair clock reference for DP data signals                          |                | N/C                                                             |              |

| GBTCLK1_M2C_P | B20 | Diff pair clock reference for DP data signals                          |                | N/C                                                             |              |

| GBTCLK0_M2C_N | D5  | Diff pair clock reference for DP data signals                          | FPGA_GBTCLK_N  | FPGA global clock -                                             | LVDS,<br>Out |

| GBTCLK0_M2C_P | D4  | Diff pair clock reference for DP data signals                          | FPGA_GBTCLK_P  | FPGA global clock +                                             | LVDS,<br>Out |

| CLK1_C2M_N    | J3  | Diff pair clock driven from host to mezzanine card                     |                | N/C                                                             |              |

| CLK1_C2M_P    | J2  | Diff pair clock driven from host to mezzanine card                     |                | N/C                                                             |              |

| CLK1_M2C_N    | К5  | Diff pair clock driven from mezzanine card to host                     |                | N/C                                                             |              |

| CLK1_M2C_P    | K4  | Diff pair clock driven from mezzanine card to host                     |                | N/C                                                             |              |

| CLK0_C2M_N    | G3  | Diff pair clock driven from host to mezzanine card                     |                | N/C                                                             |              |

| CLK0_C2M_P    | G2  | Diff pair clock driven from host to mezzanine card                     |                | N/C                                                             |              |

| CLK0_M2C_N    | H5  | Diff pair clock driven from mezzanine card to host                     | FPGA_REF_CLK_N | FPGA reference clock<br>-, AC coupled                           | LVDS,<br>Out |

| CLK0_M2C_P    | H4  | Diff pair clock driven from mezzanine card to host                     | FPGA_REF_CLK_P | FPGA reference clock<br>+, AC coupled                           | LVDS,<br>Out |

| 3P3VAUX       | D32 | 3.3V auxiliary supply                                                  | 3P3V_AUX       | Auxiliary 3.3V supply;<br>used only to power<br>EEPROM per spec | DC,<br>In    |

| VADJ3         | H40 | Adjustable voltage level power from carrier to mezzanine               | Vadj           | Vadj supply set by carrier card (1.8V to 2.5V)                  | DC,<br>In    |

| VADJ2         | G39 | Adjustable voltage level power from carrier to mezzanine               | Vadj           | Vadj supply set by carrier card (1.8V to 2.5V)                  | DC,<br>In    |

| VADJ1         | F40 | Adjustable voltage level power from carrier to mezzanine               | Vadj           | Vadj supply set by carrier card (1.8V to 2.5V)                  | DC,<br>In    |

| VADJ0         | E39 | Adjustable voltage level power from carrier to mezzanine               | Vadj           | Vadj supply set by carrier card (1.8V to 2.5V)                  | DC,<br>In    |

| 12P0V1        | C37 | Main 12V power input                                                   |                | N/C                                                             |              |

| 12P0V0      | C35 | Main 12V power input                                                                                                 |                 | N/C                                                                      |                 |

|-------------|-----|----------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------|-----------------|

| 3P3V3       | C39 | Main 3.3V power input                                                                                                | 3P3V            | Main 3.3V<br>supply for<br>card                                          | DC,<br>In       |

| 3P3V2       | D40 | Main 3.3V power input                                                                                                | 3P3V            | Main 3.3V<br>supply for<br>card                                          | DC,<br>In       |

| 3P3V1       | D38 | Main 3.3V power input                                                                                                | 3P3V            | Main 3.3V<br>supply for<br>card                                          | DC,<br>In       |

| 3P3V0       | D36 | Main 3.3V power input                                                                                                | 3P3V            | Main 3.3V<br>supply for<br>card                                          | DC,<br>In       |

| RES1        | B1  | Reserved                                                                                                             |                 | N/C                                                                      |                 |

| PRSNT_M2C_L | H2  | Module present signal – grounded                                                                                     | GND             | N/C                                                                      |                 |

| PG_C2M      | D1  | Power good for carrier, asserts high by carrier when Vadj, 12P0V, and 3P3V are within spec                           | PG_C2M          |                                                                          | In              |

| PG_M2C      | F1  | Power good mezzanine. Asserts high by the mezzanine card when VIO_B_M2C, VREF_A_M2C, and VREF_B_M2C are within spec. | FMC_MYK_PG      | Asserts<br>high when<br>all power<br>supplies<br>are within<br>tolerance | 3.3V,<br>Out    |

| RES         | B40 | Reserved, unconnected.                                                                                               |                 | N/C                                                                      |                 |

| LA00_P_CC   | G6  | User defined signal on Bank A, clock capable                                                                         |                 | N/C                                                                      |                 |

| LA00_N_CC   | G7  | User defined signal on Bank A, clock capable                                                                         |                 | N/C                                                                      |                 |

| LA01_P_CC   | D8  | User defined signal on Bank A, clock capable                                                                         |                 | N/C                                                                      |                 |

| LA01_N_CC   | D9  | User defined signal on Bank A, clock capable                                                                         |                 | N/C                                                                      |                 |

| LA02_P      | H7  | User defined signal on Bank A                                                                                        | LED_RED         | Turns on red LED                                                         | Vadj,<br>In     |

| LA02_N      | H8  | User defined signal on Bank A••••••                                                                                  | LED_GREEN       | Turns on<br>green<br>LED                                                 | Vadj,<br>In     |

| LA03_P      | G9  | User defined signal on Bank A                                                                                        | LED_BLUE        | Turns on blue LED                                                        | Vadj,<br>In     |

| LA03_N      | G10 | User defined signal on Bank A                                                                                        | FMC_SDA         | I2C serial<br>data line                                                  | Vadj,<br>In/Out |

| LA04_P      | H10 | User defined signal on Bank A                                                                                        | FMC_AD9528_CS_N | AD9528<br>SPI chip<br>select                                             | Vadj,<br>In     |

| LA04_N      | H11 | User defined signal on Bank A                                                                                        |                 | N/C                                                                      |                 |

|             |     |                                                                                                                      |                 |                                                                          |                 |

| LA05_P | D11 | User defined<br>signal on Bank<br>A | FMC_SCL            | I2C serial clock line                                                                              | Vadj,<br>In |

|--------|-----|-------------------------------------|--------------------|----------------------------------------------------------------------------------------------------|-------------|

| LA05_N | D12 | User defined<br>signal on Bank<br>A | FMC_SYSREF_REQ     | AD9528 system reference request                                                                    | Vadj,<br>In |

| LA06_P | C10 | User defined<br>signal on Bank<br>A | FMC_10M_EN         | Internal 10 MHz enable (hi=enable, low=use external 10 MHz)                                        | Vadj,<br>In |

| LA06_N | C12 | User defined<br>signal on Bank<br>A | FMC_SYSREF_REQ     | AD9528 system reference request                                                                    | Vadj,<br>In |

| LA07_P | H13 | User defined<br>signal on Bank<br>A |                    | N/C                                                                                                |             |

| LA07_N | H14 | User defined<br>signal on Bank<br>A | AD9528_SPI_RESET_N | AD9528 SPI reset                                                                                   | Vadj,<br>In |

| LA08_P | G12 | User defined<br>signal on Bank<br>A |                    | N/C                                                                                                |             |

| LA08_N | G13 | User defined<br>signal on Bank<br>A |                    | N/C                                                                                                |             |

| LA09_P | D14 | User defined<br>signal on Bank<br>A | RX_SYNCB_P         | LVDS sync signal associated with Rx channel data on the JESD204b interface                         | LVDS,<br>In |

| LA09_N | D15 | User defined<br>signal on Bank<br>A | RX_SYNCB_N         | LVDS sync signal associated with Rx channel data on the JESD204b interface LVDS, In                |             |

| LA10_P | C14 | User defined<br>signal on Bank<br>A | SNRX_SYNCB_P       | LVDS sync signal associated with ObsRx channel data on the JESD204b interface                      | LVDS,<br>In |

| LA10_N | C15 | User defined<br>signal on Bank<br>A | SNRX_SYNCB_N       | LVDS sync signal associated with ObsRx channel data on the JESD204b interface                      | LVDS,<br>In |

| LA11_P | H16 | User defined<br>signal on Bank<br>A | AD9528_SYSREF_IN_P | External SYSREF input clock                                                                        | LVDS,<br>In |

| LA11_N | H17 | User defined<br>signal on Bank<br>A | AD9528_SYSREF_IN_N | External SYSREF input clock                                                                        | LVDS,<br>In |

| LA12_P | G15 | User defined<br>signal on Bank<br>A | FMC_VCXO_153M6_EN  | Enables the 153.6 MHz reference VCXO<br>(high=153.6 MHz VCXO enabled, low=100<br>MHz VCXO enabled) | Vadj,<br>In |

| LA12_N    | G16 | User defined signal on Bank A                      |                  | N/C                                                                                                          |              |

|-----------|-----|----------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------|--------------|

| LA13_P    | D17 | User defined signal<br>on Bank A                   | FMC_REF_SEL      | Selects internal 10 or external 10 MHz<br>reference to AD9528 (low=internal 10<br>MHz, high=external 10 MHz) | Vadj,<br>Out |

| LA13_N    | D18 | User defined signal on Bank A                      |                  | N/C                                                                                                          |              |

| LA14_N    | C19 | User defined signal on Bank A                      |                  | N/C                                                                                                          |              |

| LA15_P    | H19 | User defined signal<br>on Bank A                   | TX_SYNCB_P       | LVDS sync signal associated with Tx<br>channel data on the JESD204b<br>interface                             | LVDS,<br>Out |

| LA15_N    | H20 | User defined signal<br>on Bank A                   | TX_SYNCB_N       | LVDS sync signal associated with Tx channel data on the JESD204b interface                                   | LVDS,<br>Out |

| LA16_P    | G18 | User defined signal on Bank A                      |                  | N/C                                                                                                          |              |

| LA16_P    | G19 | User defined signal on Bank A                      |                  | N/C                                                                                                          |              |

| LA17_P_CC | D20 | User defined signal<br>on Bank A, clock<br>capable | FPGA_AUX_CLK_P   | Auxiliary clock from the AD9528, AC coupled                                                                  | LVDS,<br>Out |

| LA17_N_CC | D21 | User defined signal<br>on Bank A, clock<br>capable | FPGA_AUX_CLK_N   | Auxiliary clock from the AD9528, AC coupled                                                                  | LVDS,<br>Out |

| LA18_P    | C22 | User defined signal on Bank A                      | FPGA_SYSREF_P    | FPGA SYSREF clock from AD9528                                                                                | LVDS,<br>Out |

| LA18_N    | C23 | User defined signal on Bank A                      | FPGA_SYSREF_N    | FPGA SYSREF clock from AD9528                                                                                | LVDS,<br>Out |

| LA19_P    | H22 | User defined signal on Bank A                      | FMC_EN_RXA1      | Enables the Rx1 front end LNAs                                                                               | Vadj,<br>In  |

| LA19_N    | H23 | User defined signal on Bank A                      | FMC_EN_RXA2      | Enables the Rx2 front end LNAs                                                                               | Vadj,<br>In  |

| LA20_P    | G21 | User defined signal on Bank A                      | FMC_EN_ORX       | Enables the ObsRx front end LNAs                                                                             | Vadj,<br>In  |

| LA20_N    | G22 | User defined signal on Bank A                      | FMC_EN_TX        | Enables the Tx1 output amplifier                                                                             | Vadj,<br>In  |

| LA21_P    | H25 | User defined signal on Bank A                      |                  | N/C                                                                                                          |              |

| LA21_N    | H26 | User defined signal on Bank A                      |                  | N/C                                                                                                          |              |

| LA22_P    | G24 | User defined signal on Bank A                      | FMC_PLL1_RESET_N | RF front end SPI reset for Rx1 and Rx2                                                                       | Vadj,<br>In  |

|           |     |                                                    |                  |                                                                                                              |              |

| LA22_N | G25 | User defined signal on<br>Bank A | FMC_PLL2_RESET_N | RF front end SPI reset for ObsRx and Tx1                    | Vadj,<br>In  |

|--------|-----|----------------------------------|------------------|-------------------------------------------------------------|--------------|

| LA23_P | D23 | User defined signal on<br>Bank A | RX1_ENABLE       | Enables Rx channel 1 signal path in AD9371                  | Vadj,<br>In  |

| LA23_N | D24 | User defined signal on<br>Bank A | RX2_ENABLE       | Enables Rx channel 2 signal path in AD9371                  | Vadj,<br>In  |

| LA24_P | H28 | User defined signal on<br>Bank A | TX1_ENABLE       | Enables Tx channel 1 signal path in AD9371                  | Vadj,<br>In  |

| LA24_N | H29 | User defined signal on Bank A    | TX2_ENABLE       | Enables Tx channel 2 signal path in AD9371                  | Vadj,<br>In  |

| LA25_P | G27 | User defined signal on<br>Bank A | MYK_RESET_N      | AD9371 chip reset (active low)                              | Vadj,<br>In  |

| LA25_N | G28 | User defined signal on<br>Bank A | GP_INT           | General purpose interrupt from AD9371                       | Vadj,<br>Out |

| LA26_P | D26 | User defined signal on<br>Bank A | MYK_SPI_DIN      | AD9371 + AD9528 SPI data in                                 | Vadj,<br>In  |

| LA26_N | D27 | User defined signal on<br>Bank A | MYK_SPI_DOUT     | AD9371 + AD9528 SPI data out                                | Vadj,<br>Out |

| LA27_P | C26 | User defined signal on<br>Bank A | MYK_SPI_CLK      | AD9371 + AD9528 SPI clock                                   | Vadj,<br>In  |

| LA27_N | C27 | User defined signal on<br>Bank A | MYK_SPI_CS_N     | AD9371 SPI chip select (active low)                         | Vadj,<br>In  |

| LA28_P | H31 | User defined signal on<br>Bank A | FMC_FE_MOSI      | RF front end SPI data in                                    | Vadj,<br>In  |

| LA28_N | H32 | User defined signal on<br>Bank A | FMC_FE_CLK       | RF front end SPI clock                                      | Vadj,<br>In  |

| LA29_P | G30 | User defined signal on<br>Bank A | FMC_RX1_ATT_LE   | Rx1 attenuator SPI latch enable                             | Vadj,<br>In  |

| LA29_N | G31 | User defined signal on<br>Bank A | FMC_RX2_ATT_LE   | Rx2 attenuator SPI latch enable                             | Vadj,<br>In  |

| LA30_P | H34 | User defined signal on<br>Bank A | FMC_ORX_ATT_LE   | ObsRx attenuator SPI latch enable                           | Vadj,<br>In  |

| LA30_N | H35 | User defined signal on<br>Bank A |                  | N/C                                                         |              |

| LA31_P | G33 | User defined signal on<br>Bank A | FMC_PLL1_CS_N    | RF front end SPI chip select for Rx1 and Rx2 (active low)   | Vadj,<br>In  |

| LA31_N | G34 | User defined signal on<br>Bank A | FMC_PLL2_CS_N    | RF front end SPI chip select for ObsRx and Tx1 (active low) | Vadj,<br>In  |

| LA32_P | H37 | User defined signal on<br>Bank A | FMC_MYK_PWR_EN   | Enable AD9371 power supplies                                | Vadj,<br>In  |

| LA32_N | H38 | User defined signal on<br>Bank A |                  | N/C                                                         |              |

| LA33_N | G36 | User defined signal on Bank A | N/C |

|--------|-----|-------------------------------|-----|

| LA33_N | G37 | User defined signal on Bank A | N/C |

#### Table 6: FMC Low Pin Count Pinout

# FMC HIGH PIN COUNT (HPC) SECTION

| FMC Signal<br>Name | FMC<br>Pin | FMC Description                                           | Sidekiq X2<br>Net Name | Description                   | Logic Standard,<br>I/O Type |

|--------------------|------------|-----------------------------------------------------------|------------------------|-------------------------------|-----------------------------|

| DP0_C2M_P          | C2         | Gigabit interface diff pair driven from host to mezzanine | TX_SERD0_P             | JESD204b input<br>lane for Tx | CML, In                     |

| DP0_C2M_N          | C3         | Gigabit interface diff pair driven from host to mezzanine | TX_SERD0_N             | JESD204b input<br>lane for Tx | CML, In                     |

| DP1_C2M_P          | A22        | Gigabit interface diff pair driven from host to mezzanine | TX_SERD1_P             | JESD204b input<br>lane for Tx | CML, In                     |

| DP1_C2M_N          | A23        | Gigabit interface diff pair driven from host to mezzanine | TX_SERD1_N             | JESD204b input<br>lane for Tx | CML, In                     |

| DP2_C2M_P          | A26        | Gigabit interface diff pair driven from host to mezzanine | TX_SERD2_P             | JESD204b input<br>lane for Tx | CML, In                     |

| DP2_C2M_N          | A27        | Gigabit interface diff pair driven from host to mezzanine | TX_SERD2_N             | JESD204b input<br>lane for Tx | CML, In                     |

| DP3_C2M_P          | A30        | Gigabit interface diff pair driven from host to mezzanine | TX_SERD3_P             | JESD204b input<br>lane for Tx | CML, In                     |

| DP3_C2M_N          | A31        | Gigabit interface diff pair driven from host to mezzanine | TX_SERD3_N             | JESD204b input<br>lane for Tx | CML, In                     |

| DP4_C2M_P          | A34        | Gigabit interface diff pair driven from host to mezzanine |                        | N/C                           |                             |

| DP4_C2M_N          | A35        | Gigabit interface diff pair driven from host to mezzanine |                        | N/C                           |                             |

| DP5_C2M_P          | A38        | Gigabit interface diff pair driven from host to mezzanine |                        | N/C                           |                             |

| DP5_C2M_N          | A39        | Gigabit interface diff pair driven from host to mezzanine |                        | N/C                           |                             |

| DP6_C2M_P          | B36        | Gigabit interface diff pair driven from host to mezzanine |                        | N/C                           |                             |

| DP6_C2M_N          | B37        | Gigabit interface diff pair driven from host to mezzanine |                        | N/C                           |                             |

| DP7_C2M_P | B32 | Gigabit interface diff pair driven from host to mezzanine |            | N/C                            |             |

|-----------|-----|-----------------------------------------------------------|------------|--------------------------------|-------------|

| DP7_C2M_N | B33 | Gigabit interface diff pair driven from host to mezzanine |            | N/C                            |             |

| DP8_C2M_P | B28 | Gigabit interface diff pair driven from host to mezzanine |            | N/C                            |             |

| DP8_C2M_N | B29 | Gigabit interface diff pair driven from host to mezzanine |            | N/C                            |             |

| DP9_C2M_P | B24 | Gigabit interface diff pair driven from host to mezzanine |            | N/C                            |             |

| DP9_C2M_N | B25 | Gigabit interface diff pair driven from host to mezzanine |            | N/C                            |             |

| DP0_M2C_P | C6  | Gigabit interface diff pair driven from mezzanine to host | RX_SERD0_P | JESD204b output<br>lane for Rx | CML,<br>Out |

| DP0_M2C_N | C7  | Gigabit interface diff pair driven from mezzanine to host | RX_SERD0_N | JESD204b output<br>lane for Rx | CML,<br>Out |

| DP1_M2C_P | A2  | Gigabit interface diff pair driven from mezzanine to host | RX_SERD1_P | JESD204b output<br>lane for Rx | CML,<br>Out |

| DP1_M2C_N | A3  | Gigabit interface diff pair driven from mezzanine to host | RX_SERD1_N | JESD204b output<br>lane for Rx | CML,<br>Out |

| DP2_M2C_P | A6  | Gigabit interface diff pair driven from mezzanine to host | RX_SERD2_P | JESD204b output<br>lane for Rx | CML,<br>Out |

| DP2_M2C_N | A7  | Gigabit interface diff pair driven from mezzanine to host | RX_SERD2_N | JESD204b output<br>lane for Rx | CML,<br>Out |

| DP3_M2C_P | A10 | Gigabit interface diff pair driven from mezzanine to host | RX_SERD3_P | JESD204b output<br>lane for Rx | CML,<br>Out |

| DP3_M2C_N | A11 | Gigabit interface diff pair driven from mezzanine to host | RX_SERD3_N | JESD204b output<br>lane for Rx | CML,<br>Out |

| DP4_M2C_P | A14 | Gigabit interface diff pair driven from mezzanine to host |            | N/C                            |             |

| DP4_M2C_N | A15 | Gigabit interface diff pair driven from mezzanine to host |            | N/C                            |             |

| DP5_M2C_P | A18 | Gigabit interface diff pair driven from mezzanine to host |            | N/C                            |             |

| DP5_M2C_N | A19 | Gigabit interface diff pair driven from mezzanine to host |            | N/C                            |             |

| DP6_M2C_P | B16 | Gigabit interface diff pair driven from mezzanine to host |            | N/C                            |             |

| DP6_M2C_N | B17 | Gigabit interface diff pair driven from mezzanine to host |            | N/C                            |             |

| DP7_M2C_P | B12 | Gigabit interface diff pair driven from mezzanine to host |            | N/C                            |             |

| DP7_M2C_N | B13 | Gigabit interface diff pair driven from mezzanine to host                               |            | N/C                                  |                 |

|-----------|-----|-----------------------------------------------------------------------------------------|------------|--------------------------------------|-----------------|

| DP8_M2C_P | B8  | Gigabit interface diff pair driven from mezzanine to host                               |            | N/C                                  |                 |

| DP8_M2C_N | В9  | Gigabit interface diff pair driven from mezzanine to host                               |            | N/C                                  |                 |

| DP9_M2C_P | B4  | Gigabit interface diff pair driven from mezzanine to host                               |            | N/C                                  |                 |

| DP9_M2C_N | В5  | Gigabit interface diff pair driven from mezzanine to host                               |            | N/C                                  |                 |

| HA00_P_CC | F4  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C (clock capable) | MYK_GPIO0  | AD9371 GPIO<br>referenced to<br>Vadj | Vadj,<br>In/Out |

| HA00_N_CC | F5  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C (clock capable) | MYK_GPIO1  | AD9371 GPIO<br>referenced to<br>Vadj | Vadj,<br>In/Out |

| HA01_P_CC | E2  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C (clock capable) | MYK_GPIO2  | AD9371 GPIO<br>referenced to<br>Vadj | Vadj,<br>In/Out |

| HA01_N_CC | E3  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C (clock capable) | MYK_GPIO3  | AD9371 GPIO<br>referenced to<br>Vadj | Vadj,<br>In/Out |

| HA02_P    | K7  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 | MYK_GPIO4  | AD9371 GPIO<br>referenced to<br>Vadj | Vadj,<br>In/Out |

| HA02_N    | K8  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 | MYK_GPIO5  | AD9371 GPIO<br>referenced to<br>Vadj | Vadj,<br>In/Out |

| HA03_P    | J6  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA03_N    | J7  | User defined signal on Bank A, uses reference voltage on pin VREFAM2C                   |            | N/C                                  |                 |

| HA04_P    | F7  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 | MYK_GPIO6  | AD9371 GPIO<br>referenced to<br>Vadj | Vadj,<br>In/Out |

| HA04_N    | F8  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 | MYK_GPIO7  | AD9371 GPIO<br>referenced to<br>Vadj | Vadj,<br>In/Out |

| HA05_P    | E6  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 | MYK_GPIO8  | AD9371 GPIO<br>referenced to<br>Vadj | Vadj,<br>In/Out |

| HA05_N    | E7  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 | MYK_GPIO15 | AD9371 GPIO<br>referenced to<br>Vadj | Vadj,<br>In/Out |

| HA06_P | K10 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C | MYK_GPIO9  | AD9371 GPIO<br>referenced to Vadj | Vadj,<br>In/Out |

|--------|-----|-------------------------------------------------------------------------|------------|-----------------------------------|-----------------|

| HA06_N | K11 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C | MYK_GPIO10 | AD9371 GPIO<br>referenced to Vadj | Vadj,<br>In/Out |

| HA07_P | J9  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            | N/C                               |                 |

| HA07_N | J10 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            | N/C                               |                 |

| HA08_P | F10 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C | MYK_GPI011 | AD9371 GPIO<br>referenced to Vadj | Vadj,<br>In/Out |

| HA08_N | F11 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C | MYK_GPIO12 | AD9371 GPIO<br>referenced to Vadj | Vadj,<br>In/Out |

| HA09_P | E9  | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            | N/C                               |                 |

| HA09_N | E10 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C | MYK_GPIO18 | AD9371 GPIO<br>referenced to Vadj | Vadj,<br>In/Out |

| HA10_P | K13 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            | N/C                               |                 |

| HA10_P | K14 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            | N/C                               |                 |

| HA11_P | J12 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            | N/C                               |                 |

| HA11_P | J13 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            | N/C                               |                 |

| HA12_P | F13 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            | N/C                               |                 |

| HA12_N | F14 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            | N/C                               |                 |

| HA13_P | E12 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C | MYK_GPIO13 | AD9371 GPIO<br>referenced to Vadj | Vadj,<br>In/Out |

| HA13_N | E13 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C | MYK_GPIO14 | AD9371 GPIO<br>referenced to Vadj | Vadj,<br>In/Out |

| HA14_P | J15 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            |                                   |                 |

| HA14_N | J16 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            |                                   |                 |

| HA15_P | F16 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            |                                   |                 |

| HA15_N | F17 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C |            |                                   |                 |

| HA16_P | E15 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C | MYK_GPIO16 | AD9371 GPIO<br>referenced to Vadj | Vadj,<br>In/Out |

| HA16_N    | E16 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 | MYK_GPIO17 | AD9371 GPIO<br>referenced to<br>Vadj | Vadj,<br>In/Out |

|-----------|-----|-----------------------------------------------------------------------------------------|------------|--------------------------------------|-----------------|

| HA17_P_CC | K16 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C (clock capable) |            | N/C                                  |                 |

| HA17_P_CC | K17 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C (clock capable) |            | N/C                                  |                 |

| HA18_P    | J18 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA18_N    | J19 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA19_P    | F19 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA19_N    | F20 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA20_P    | E18 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA20_N    | E19 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA21_P    | K19 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA21_N    | K20 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA22_P    | J21 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA22_N    | J22 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA23_P    | K22 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HA23_N    | K23 | User defined signal on Bank A, uses reference voltage on pin VREF_A_M2C                 |            | N/C                                  |                 |

| HB00_P_CC | K25 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C (clock capable) |            | N/C                                  |                 |

| HB00_N_CC | K26 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C (clock capable) |            | N/C                                  |                 |

| HB01_P    | J24 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C                 |            | N/C                                  |                 |

| HB01_N    | J25 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C                 |            | N/C                                  |                 |

| HB02_P    | F22 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C                 |            | N/C                                  |                 |

| HB02_N    | F23 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

|-----------|-----|-------------------------------------------------------------------------|-----|

| HB03_P    | E21 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB03_N    | E22 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB04_P    | F25 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB04_N    | F26 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB05_P    | E24 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB05_N    | E25 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB06_P    | K28 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB06_N    | K29 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB07_P    | J27 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB07_N    | J28 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB08_P    | F28 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB08_N    | F29 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB09_P    | E27 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB09_N    | E28 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB10_P    | K31 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB10_N    | K32 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB11_P    | J30 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB11_N    | J31 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB12_P    | F31 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB12_N    | F32 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB13_P    | E30 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB13_N    | E31 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB14_P    | K34 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB14_N    | K35 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB15_P    | J33 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB15_N    | J34 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB16_P    | F34 | User defined signal on Bank A, uses reference voltage on pin VREFBM2C   | N/C |

| HB16_N    | F35 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB17_P_CC | K37 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB17_N_CC | K38 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB18_P    | J36 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

|           |     |                                                                         |     |

| HB18_N | J37 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

|--------|-----|-------------------------------------------------------------------------|-----|

| HB19_P | E33 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB19_N | E34 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB20_P | F37 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB20_N | F38 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

| HB21_P | E36 | User defined signal on Bank A, uses reference voltage on pin VREFBM2C   | N/C |

| HB21_N | E37 | User defined signal on Bank A, uses reference voltage on pin VREF_B_M2C | N/C |

Table 7: FMC High Pin Count Pinout

# **BASIC USAGE IN A HOST SYSTEM**

### HOST SYSTEM COMPATIBILITY

Sidekiq X2 is expected to be deployed into a host system that adheres to a general architecture in order to utilize the core FPGA reference design and associated libsidekiq software API. This general architecture is shown in Figure 5 below.

Figure 5: General Sidekiq X2 deployment architecture

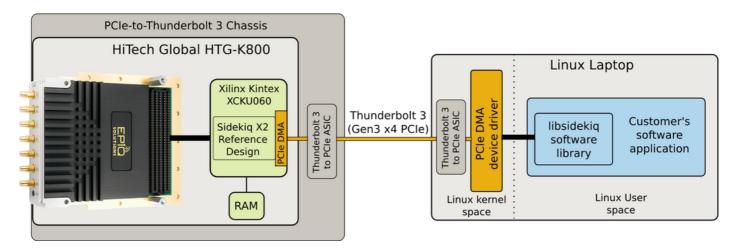

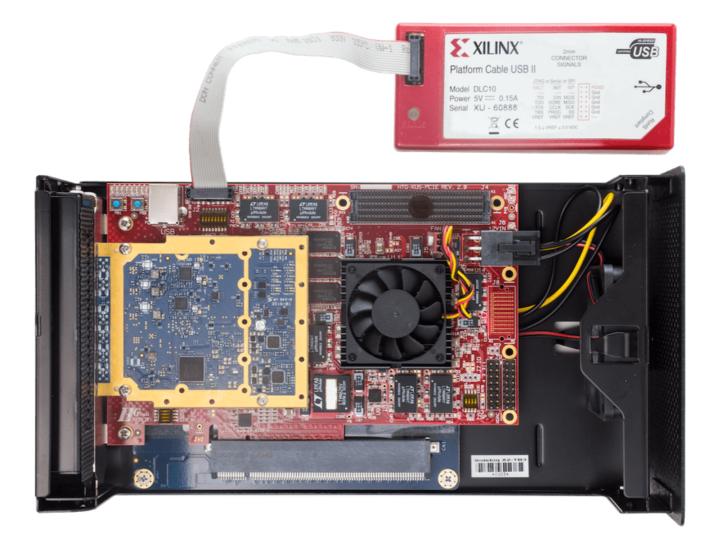

A typical deployment scenario into a host platform is shown in Figure 6, which depicts the Sidekiq X2 plugged into a COTS PCIe FPGA board (HiTech Global's HTG-K800 [5]), mounted into a Thunderbolt 3 chassis, connected to a host computer running Linux through a Thunderbolt 3 cable. In this deployment, the FPGA on the HTG-K800 is the Xilinx Kintex Ultrascale XCKU060, and a Gen3 x4 PCIe interface native to the FPGA is utilized to provide the transport between the FPGA and host computer via the Thunderbolt 3 chassis. On the host computer, a Linux device driver supports both PCIe register reads/writes as well as DMA between the FPGA and the CPU in the host computer. The libsidekiq API then uses PCIe as the transport layer to support all of the standard Sidekiq API calls.

Figure 6: Sidekiq X2 deployment architecture with PCIe carrier, Thunderbolt 3 chassis, and a host Linux PC

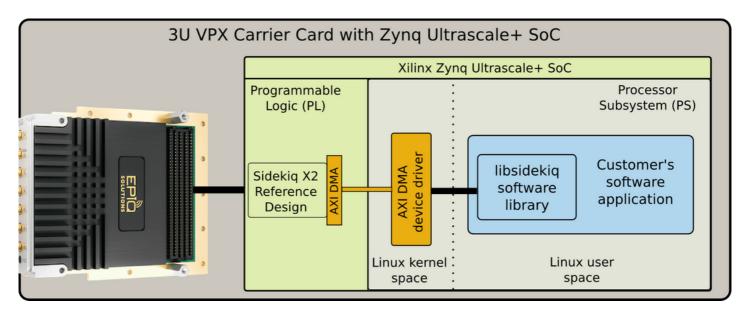

In an alternate deployment scenario, Sidekiq X2 can be interfaced to a 3U VPX carrier card that hosts an integrated FPGA + CPU in a single chip, such as the Xilinx Zynq Ultrascale+ SoC. In this scenario, both the FPGA fabric required to execute the Sidekiq X2 FPGA reference design and the multi-core ARM CPU running the libsidekiq software library are located on a single device (i.e., the Zynq Ultrascale+ SoC). The transport layer used to interface between the Zynq's FPGA fabric (PL) and the Zynq's ARM CPU (PS) is an efficient AXI-based DMA interconnect. This is shown in Figure 7 below.

Figure 7: Sidekiq X2 deployment architecture with a Zynq Ultrascale+ SoC

Note that this configuration with the Zynq Ultrascale+ SoC in a 3U VPX platform could also use PCIe as the transport to interface to the VPX backplane. In this configuration, the AXI transport is no longer needed, and all transport activities would be targeting a 3U VPX computer card plugged into the 3U VPX backplane, similar to the architecture shown in Figure 6.

#### **OPERATING SYSTEM COMPATIBILITY**

Linux is the only operating system that is currently supported. Various kernel versions have been tested starting at Linux version 3.0. Sidekiq has been tested both in x86-based Linux systems as well as ARM-based Linux systems. Kernel versions prior to 3.0 (i.e., 2.6+) may also be supported.

For customers interested in doing a custom build of the Sidekiq PCIe device driver for their host platform, a license for the source code for this device driver is also available separately. Please contact Epiq Solutions for details.

Alternate operating systems, such as Windows, may also be supported in the future. Please contact Epiq Solutions for details.